# fit-PC3 / fit-PC3i

**Hardware Specification**

## **Legal Notice**

© 2013 CompuLab Ltd.

All Rights Reserved. No part of this document may be photocopied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means whether, electronic, mechanical, or otherwise without the prior written permission of CompuLab Ltd.

No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by CompuLab Ltd., its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

CompuLab Ltd. reserves the right to change details in this publication without notice.

Product and company names herein may be the trademarks of their respective owners.

CompuLab Ltd. 17 HaYetsira St., Yokneam Elite 20692, P.O.B 687 **ISRAEL**

Tel: +972-4-8290100 http://www.compulab.co.il http://fit-pc.com/web/

Fax: +972-4-8325251

## **Revision History**

| Revision | Engineer     | Revision Changes                             |  |

|----------|--------------|----------------------------------------------|--|

| 1.0      | Maxim Birger | Initial public release                       |  |

| 1.1      | Maxim Birger | Added power supply temperature ratings: 10.2 |  |

|          |              |                                              |  |

|          |              |                                              |  |

|          |              |                                              |  |

## **Table of Contents**

| Le | egal No | tice                                   | 2  |

|----|---------|----------------------------------------|----|

| R  | evision | History                                | 3  |

| 1  | Intr    | oduction                               | 9  |

|    | 1.1     | About This Document                    | 9  |

|    | 1.2     | Reference                              | 9  |

|    | 1.3     | Terms and Acronyms                     | 10 |

| 2  | Syst    | em Overview                            | 11 |

|    | 2.1     | Highlights                             | 11 |

|    | 2.2     | Specifications                         | 11 |

|    | 2.3     | System Block Diagram                   | 14 |

|    | 2.4     | Models and Platform SKUs               | 15 |

| 3  | Plat    | form                                   | 16 |

|    | 3.1     | Processor                              | 16 |

|    | 3.1.1   | Processor Features                     | 16 |

|    | 3.2     | Graphics Processor                     | 17 |

|    | 3.2.1   | Graphics Features                      | 17 |

|    | 3.2.2   | Display Interface                      | 17 |

|    | 3.2.3   | APU PCI Express* Controller            | 18 |

|    | 3.3     | Chipset                                | 19 |

|    | 3.3.1   | Unified Media Interface (UMI)          | 20 |

|    | 3.3.2   | FCH PCI Express* Controller            | 20 |

|    | 3.3.3   | PCI Host Bus Controller                | 20 |

|    | 3.3.4   | Serial ATA (SATA) Controller           | 20 |

|    | 3.3.4.1 | AHCI                                   | 21 |

|    | 3.3.5   | Low Pin Count (LPC) Bridge             | 22 |

|    | 3.3.6   | Universal Serial Bus (USB) Controllers | 24 |

|    | 3.3.7   | RTC                                    | 25 |

|    | 3.3.8   | GPIO                                   | 25 |

|    | 3.3.9   | System Management Bus (SMBus)          | 25 |

|    | 3.3.10  | High Definition Audio Controller       | 26 |

|    | 3.3.11  | Integrated Clock Controller            | 26 |

|   | 3.4     | System Memory                          | 27 |

|---|---------|----------------------------------------|----|

|   | 3.4.1   | Processor Integrated Memory Controller | 27 |

|   | 3.4.2   | System Supported Memory                | 28 |

|   | 3.4.3   | System Memory Timing Support           | 29 |

|   | 3.4.4   | System Memory Organization Modes       | 29 |

|   | 3.4.5   | Rules for Populating Memory Slots      | 29 |

|   | 3.5     | Storage                                | 30 |

|   | 3.5.1   | Certified storage devices              | 31 |

|   | 3.5.1.1 | HDD examples                           | 31 |

|   | 3.5.1.2 | mSATA SSD examples                     | 35 |

| 4 | Peri    | pherals                                | 37 |

|   | 4.1     | USB3.0 Host Controller                 | 37 |

|   | 4.2     | Network                                | 38 |

|   | 4.2.1   | Realtek RTL8111F GbE Controller        | 38 |

|   | 4.2.1.1 | Realtek RTL8111F Features              | 38 |

|   | 4.2.1.2 | LAN Ports LEDs notifications           | 39 |

|   | 4.3     | Wireless Networks                      | 39 |

|   | 4.4     | Wireless Module Features               | 39 |

|   | 4.4.1   | WLAN                                   | 41 |

|   | 4.4.2   | Bluetooth                              | 41 |

|   | 4.4.3   | Security                               | 41 |

|   | 4.5     | Audio                                  | 42 |

|   | 4.5.1   | Audio Codec General Description        | 42 |

|   | 4.5.2   | Audio Codec Features                   | 42 |

|   | 4.6     | Super-I/O Controller                   | 45 |

| 5 | Inte    | rfaces                                 | 46 |

|   | 5.1     | PCI Express*                           | 46 |

|   | 5.1.1   | PCI Express* Architecture              | 46 |

|   | 5.1.2   | PCI Express* Specifications            | 46 |

|   | 5.1.3   | Mini PCI Express* Edge Connector       | 47 |

|   | 5.2     | Unified Media Interface (UMI)          | 48 |

|   | 5.2.1   | UMI Specifications                     | 48 |

|    | 5.3     | Digital Display Interface                   | . 48 |

|----|---------|---------------------------------------------|------|

|    | 5.3.1   | High Definition Multimedia Interface (HDMI) | 48   |

|    | 5.3.1.1 | HDMI Connector                              | 49   |

|    | 5.3.2   | Digital Video Interface (DVI)               | 50   |

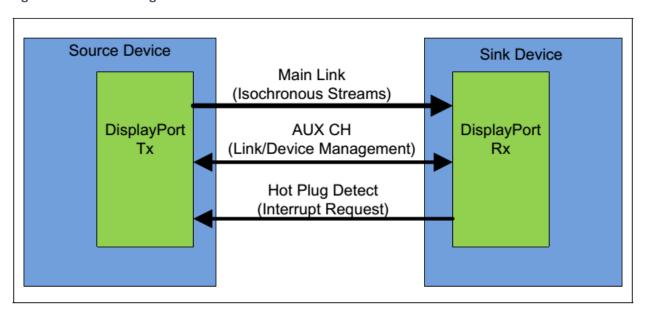

|    | 5.3.3   | Display Port Interface (DP)                 | 50   |

|    | 5.3.3.1 | DisplayPort Connector                       | 52   |

|    | 5.4     | Analog Display Interface                    | 55   |

|    | 5.4.1   | VGA DB15 Connector                          | 55   |

|    | 5.5     | RS232 Serial Interface                      | 56   |

| 6  | Misc    | cellaneous Features                         | 57   |

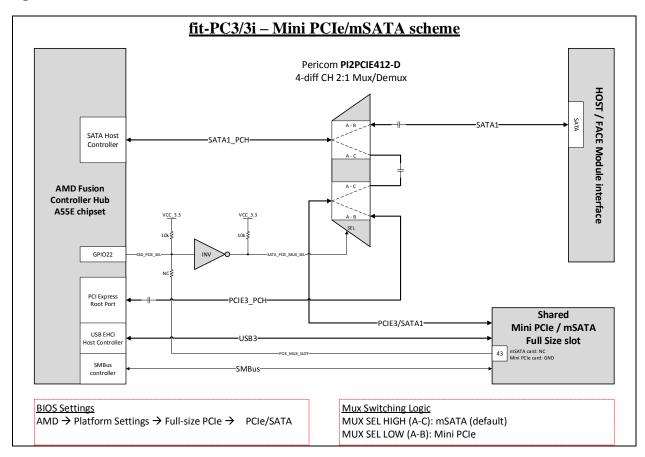

|    | 6.1     | Mini PCI Express/mSATA sharing              | 57   |

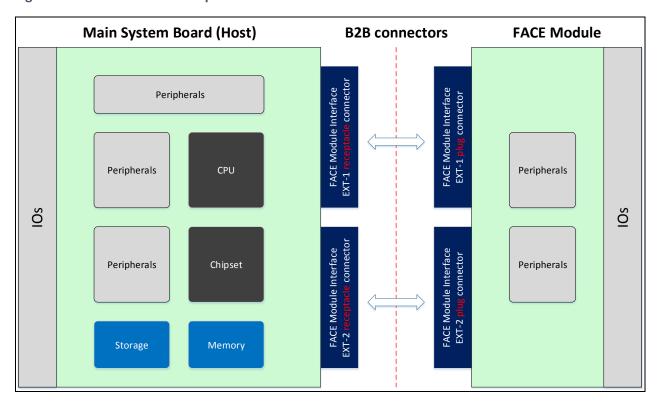

|    | 6.2     | FACE Module Interface                       | 58   |

|    | 6.2.1   | Extension Connectors                        | 59   |

|    | 6.2.2   | Connectors Pinout                           | . 60 |

|    | 6.3     | Custom Design GPIOs                         | 63   |

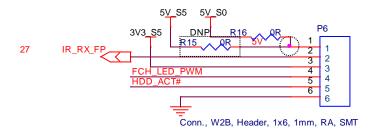

|    | 6.4     | Misc Use Connector                          | . 64 |

| 7  | Adv     | anced Technologies                          | . 65 |

|    | 7.1     | AMD Virtualization Technology               | 65   |

| 8  | Pow     | ver Management                              | . 66 |

|    | 8.1     | Power Manager                               | . 66 |

| 9  | Elec    | trical Characteristics                      | . 67 |

|    | 9.1     | Absolute Maximum Ratings                    | 67   |

|    | 9.2     | Recommended Operating Conditions            | . 67 |

|    | 9.3     | DC Electrical Characteristics               | 67   |

|    | 9.4     | Power Supply                                | . 67 |

| 1( | ) M     | Nechanical Characteristics                  | . 68 |

|    | 10.1    | Mechanical Drawings                         | . 68 |

|    | 10.1.1  | Fit-PC3 Pro                                 | . 68 |

|    | 10.1.2  | Fit-PC3 LP                                  | 71   |

|    | 10.1.3  | Fit-PC3i                                    | 74   |

|    | 10.1.4  | Single Board Computer                       | 75   |

|    | 10.1.4. | .1 With FACE Module                         | 75   |

| 10.1.4.2 Without FACE Module                         | 75                   |

|------------------------------------------------------|----------------------|

| 10.2 Environmental                                   | 76                   |

| 11 Resources                                         | 77                   |

|                                                      |                      |

|                                                      |                      |

|                                                      |                      |

|                                                      |                      |

| Table of Figures                                     |                      |

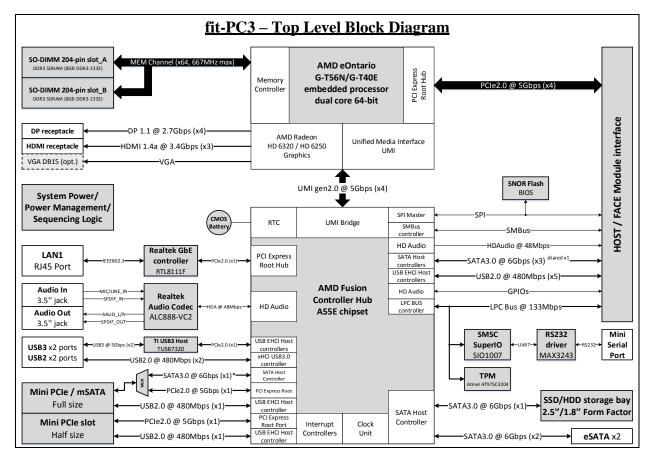

| Figure 1 – fit-PC3 Top Level Block Diagram           | 14                   |

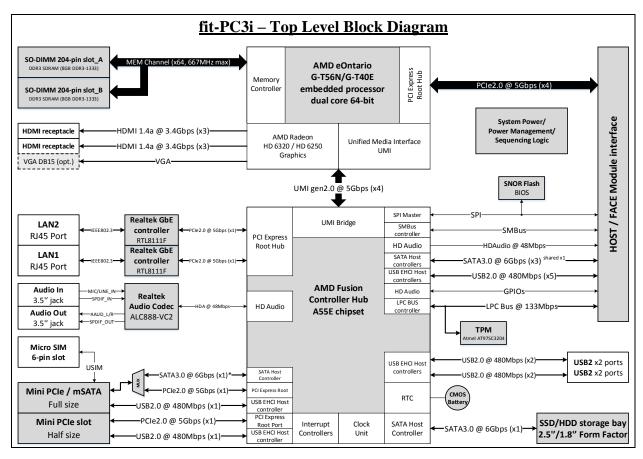

| Figure 2 – fit-PC3i Top Level Block Diagram          | 15                   |

| Figure 3 – Block Diagram for the SATA Module         | 21                   |

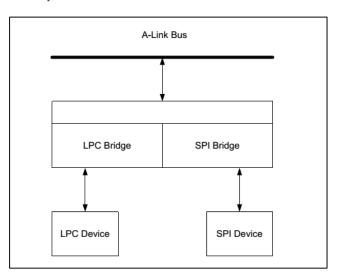

| Figure 4 – Typical LPC Bus System                    | 22                   |

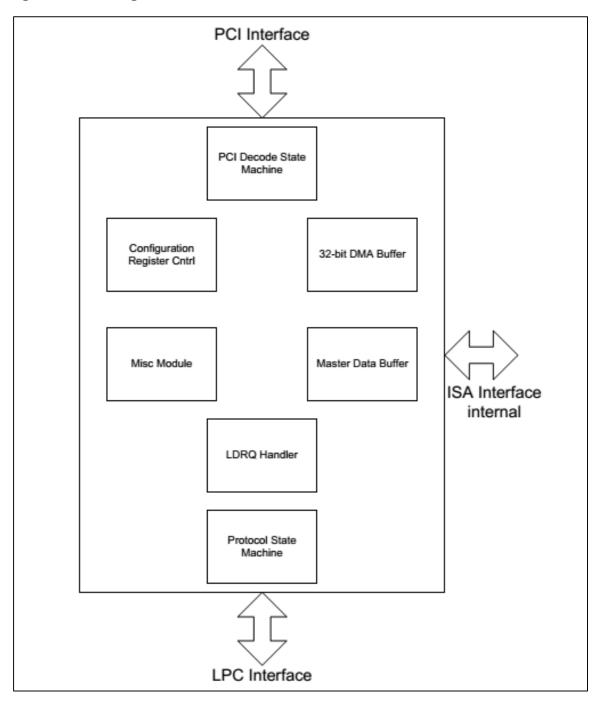

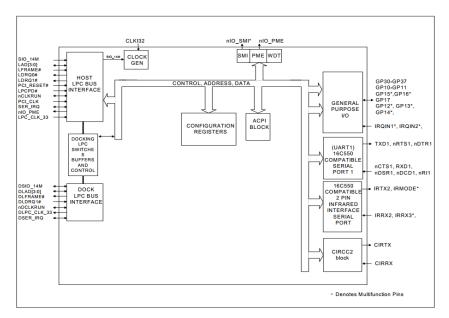

| Figure 5 – Block Diagram of LPC Module               | 23                   |

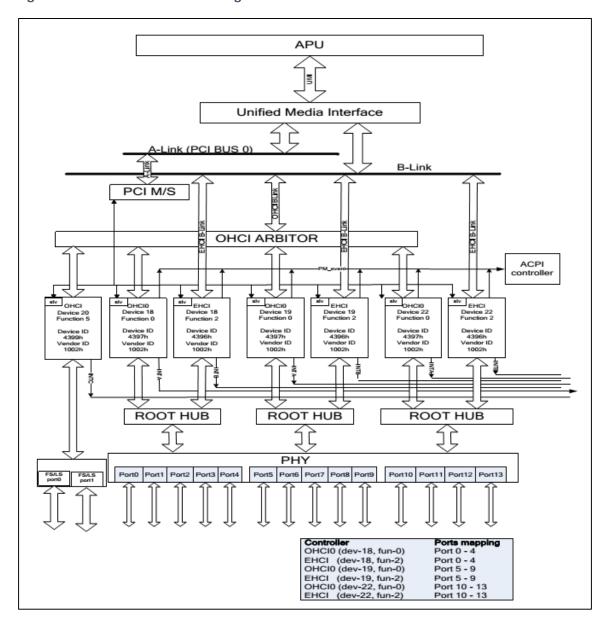

| Figure 6 – USB Controllers Block Diagram             | 24                   |

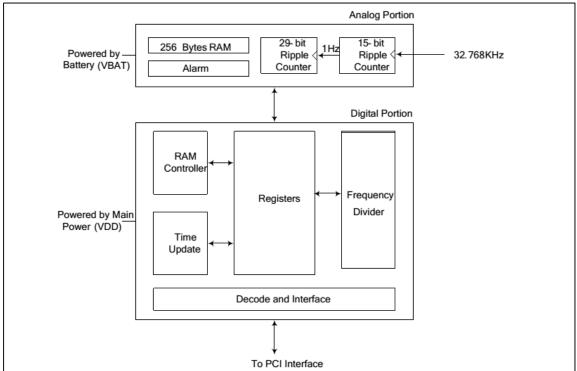

| Figure 7 – RTC Block Diagram                         | 25                   |

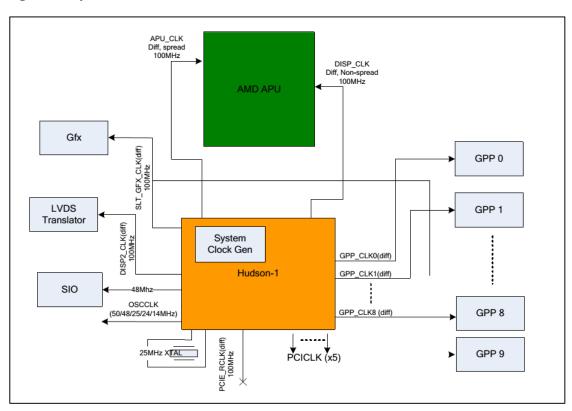

| Figure 8 – System Clock Generation                   | 26                   |

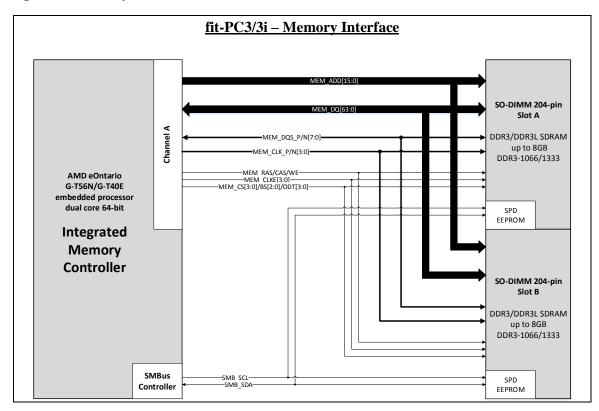

| Figure 9 – Memory Interface                          | 27                   |

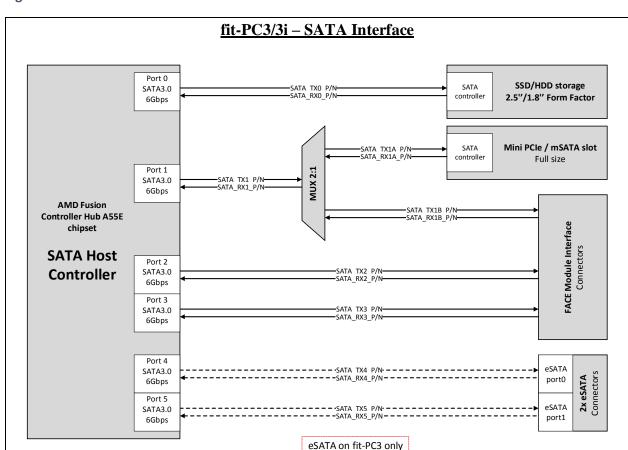

| Figure 10 – SATA Interface                           | 30                   |

| Figure 11 – Wireless Module Q802XRN5B Block Diagra   | am40                 |

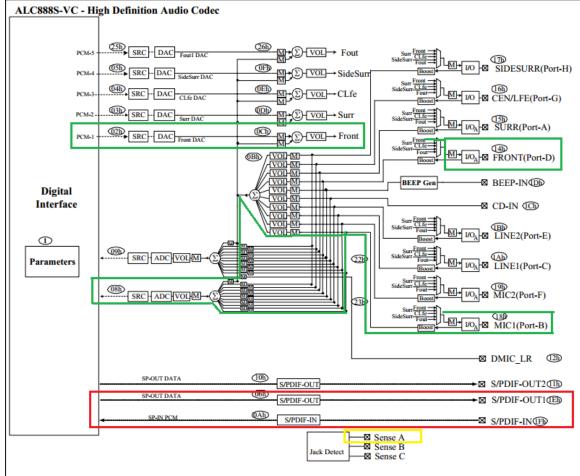

| Figure 12 – Audio Codec Functional Block Diagram     | 44                   |

| Figure 13 – SMSC SIO1007 Super-I/O Controller functi | onal block diagram45 |

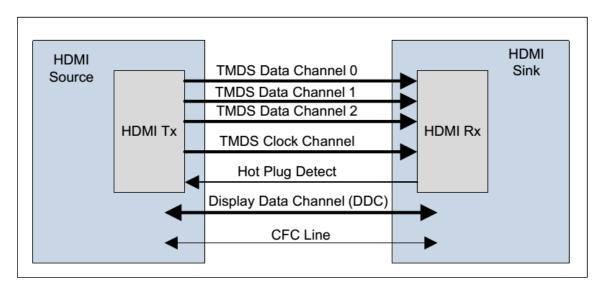

| Figure 14 – HDMI Link Diagram                        | 49                   |

| Figure 15 – DP Link Diagram                          | 51                   |

| Figure 16 – COM1 Serial Port Pinout                  | 56                   |

| Figure 17 – fit-PC3/3i PC Mini PCIe/mSATA scheme     | 57                   |

| Figure 18 – FACE Module concept                      | 58                   |

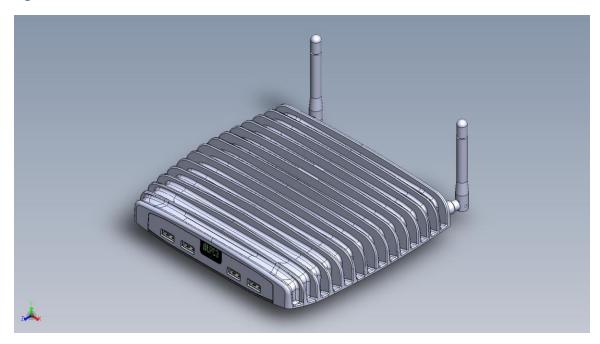

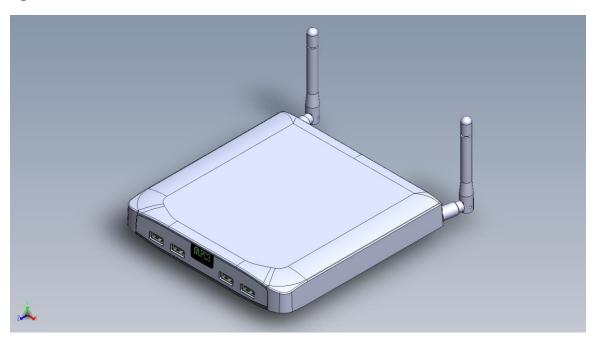

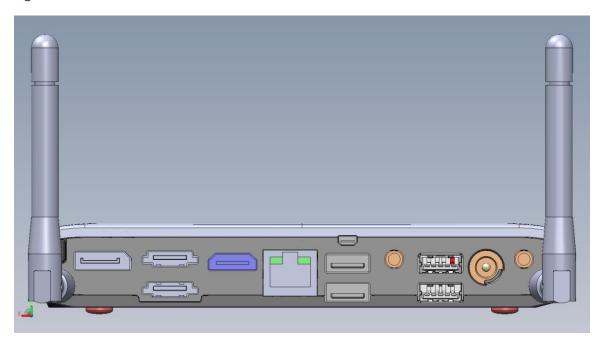

| Figure 19 – fit-PC3 Pro Isometric Front              | 68                   |

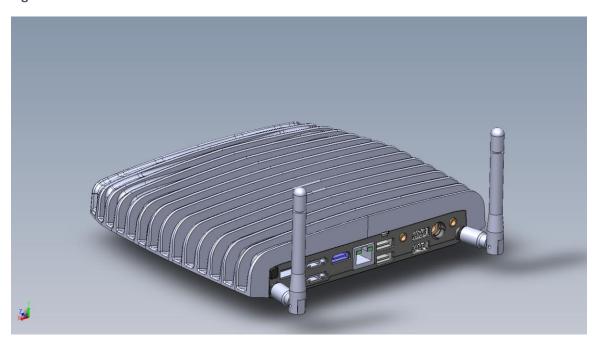

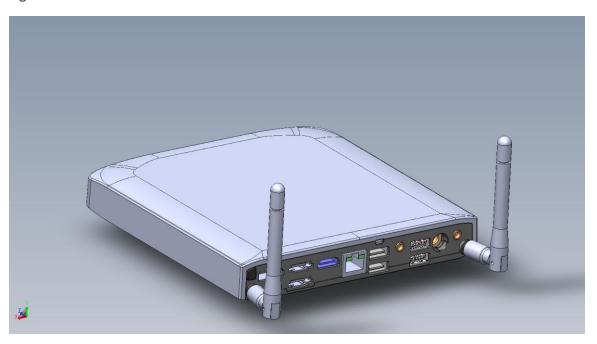

| Figure 20 – fit-PC3 Pro Isometric Back               | 68                   |

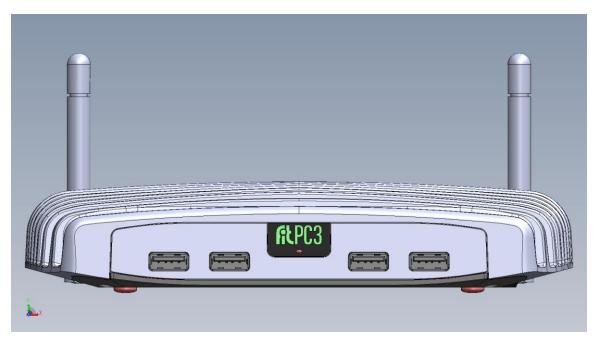

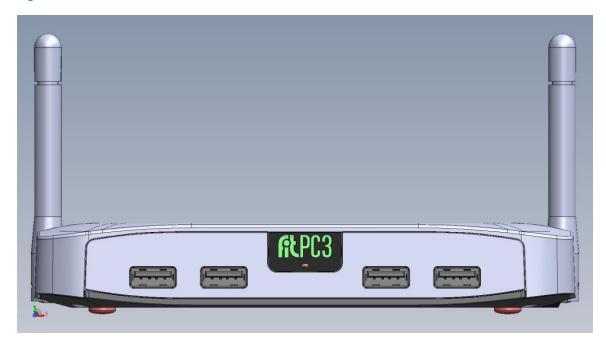

| Figure 21 – fit-PC3 Pro Front Panel                  |                      |

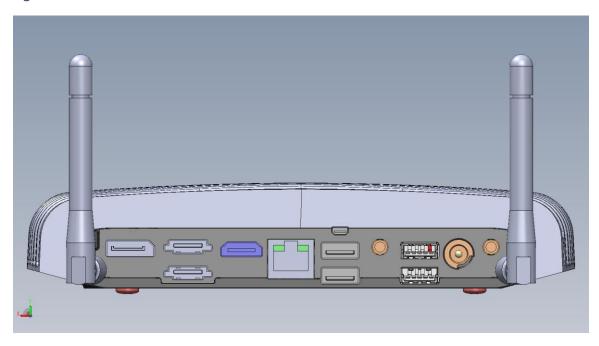

| Figure 22 – fit-PC3 Pro Back Panel                   |                      |

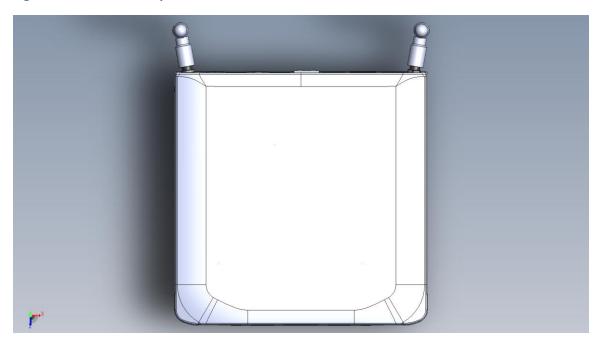

| Figure 23 – fit-PC3 Pro Top                          | 70                   |

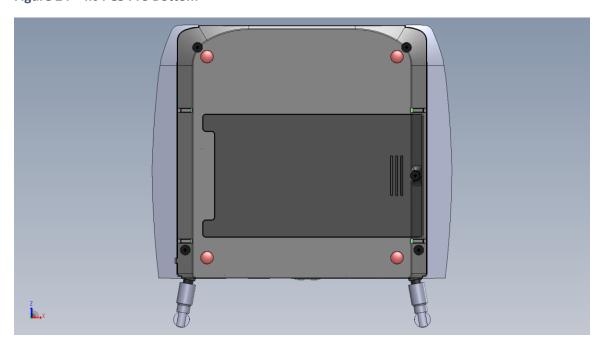

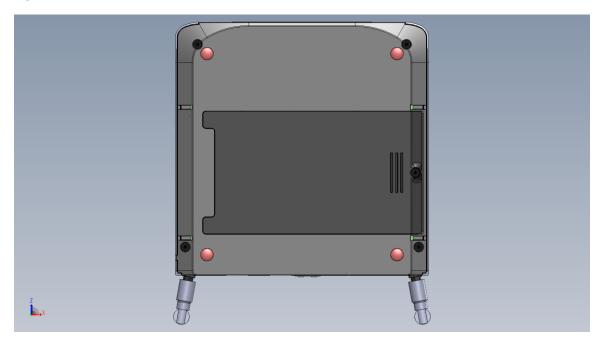

| Figure 24 – fit-PC3 Pro Bottom                       |                      |

| Figure 25 – fit-PC3 LP Isometric Front               |                      |

| Figure 26 – fit-PC3 LP Isometric Back                |                      |

| Figure 27 – fit-PC3 LP Front Panel                   |                      |

| Figure 28 – fit-PC3 LP Back Panel                    |                      |

| Figure 29 – fit-PC3 LP Top                           |                      |

| Figure 30 – fit-PC3 LP Bottom                        |                      |

| Figure 31 – fit-PC3i Pro Back Panel                  |                      |

| Figure 32 – SBC-FITPC3 Mechanical Drawing with FAC   |                      |

| Figure 33 – SBC-FITPC3 Mechanical Drawing without I  |                      |

| U                                                    |                      |

## Table of Tables

| Table 1 – Reference Documents                                | 9  |

|--------------------------------------------------------------|----|

| Table 2 – Terms and Acronyms                                 | 10 |

| Table 3 – Platform Specifications                            | 11 |

| Table 4 – Display and Graphics Specifications                | 12 |

| Table 5 – Audio Specifications                               | 12 |

| Table 6 – Networking Specifications                          | 12 |

| Table 7 – Connectivity Specifications                        | 13 |

| Table 8 – Mechanical and Environmental Specifications        | 13 |

| Table 9 – Models and Platform SKUs                           | 15 |

| Table 10 – Supported Memory Technologies                     | 28 |

| Table 11 – Supported Max Memory Size per SO-DIMM             | 29 |

| Table 12 – DDR3 System Memory Timing Support                 | 29 |

| Table 13 – WD Scorpio Blue HDD series                        | 31 |

| Table 14 – WD Scorpio Blue HDD series (cont.)                | 32 |

| Table 15 – Hitachi CinemaStar C5K750 HDD models              | 33 |

| Table 16 – Seagate Momentus HDD series                       | 34 |

| Table 17 – Micron mSATA NAND Flash SSD                       | 35 |

| Table 18 – ACPI CMS2G-M SSD                                  | 36 |

| Table 19 – LAN ports LEDs status notification                | 39 |

| Table 20 – WLAN Channel Assignment                           | 41 |

| Table 21 – BT Channel Assignment                             | 41 |

| Table 22 – mini PCI Express edge connector pinout            | 47 |

| Table 23 – Downstream Port HDMI Connector Pinout             | 49 |

| Table 24 – Downstream Port HDMI Connector Signal Description | 50 |

| Table 25 – Downstream Port DP Connector Pinout               | 52 |

| Table 26 – Upstream Port DP Connector Pinout                 | 53 |

| Table 27 – Display Port Cable                                | 54 |

| Table 28 – VGA DB15 Connector                                | 55 |

| Table 29 – B2B receptacle connector HOST side                | 59 |

| Table 30 – B2B plug connector FACE Module side               | 59 |

| Table 31 – EXT1 connector HOST side pinout                   | 60 |

| Table 32 – EXT2 connector HOST side pinout                   | 61 |

| Table 33 – Custom Design GPIO table                          |    |

| Table 34 – Misc Use Connector                                | 64 |

| Table 35 – Absolute Maximum Ratings                          | 67 |

| Table 36 – Recommended Operating Condition                   |    |

| Table 37 – DC Electrical Characteristics                     |    |

| Table 38 – Operating Temperature Grades                      | 76 |

## 1 Introduction

#### 1.1 About This Document

This document is part of a set of reference documents providing information necessary to operate Compulab's fit-PC3 and fit-PC3i computers.

#### 1.2 Reference

For additional information not covered in this manual, please refer to the documents listed in *Table 1*.

Table 1 - Reference Documents

| Document                      | Location                                                                                 |

|-------------------------------|------------------------------------------------------------------------------------------|

| FACE Module HW Specifications | http://fit-pc.com/download/face-<br>modules/documents/face-modules-hw-specifications.pdf |

|                               | modules/ documents/ race-modules-nw-specifications.pdf                                   |

| AMD Virtualization Technology | http://sites.amd.com/uk/business/it-                                                     |

|                               | solutions/virtualization/Pages/amd-v.aspx                                                |

|                               |                                                                                          |

|                               |                                                                                          |

## 1.3 Terms and Acronyms

## Table 2 – Terms and Acronyms

| Term        | Definition                                                    |  |

|-------------|---------------------------------------------------------------|--|

| APM         | Advanced Power Management                                     |  |

| APU         | Accelerated Processing Unit                                   |  |

| B2B         | Board to Board (connectors)                                   |  |

| BER         | Bit error rate                                                |  |

| bps         | Bits per second                                               |  |

| BT          | Bluetooth                                                     |  |

| CAN         | Controller Area Network                                       |  |

| Codec       | Coder decoder                                                 |  |

| DDR         | Dual data rate                                                |  |

| DMA         | Direct Memory Access                                          |  |

| DSP         | Digital signal processor                                      |  |

| FACE Module | Function And Connectivity Extension Module                    |  |

| FCH         | Platform Controller Hub                                       |  |

| FM-xxxx     | FACE Module – connectivity options                            |  |

| GB/s        | Gigabytes per second                                          |  |

| GPIO        | General-purpose input/output                                  |  |

| GT/s        | Giga Transfers per second (throughput)                        |  |

| HW          | Hardware                                                      |  |

| JTAG        | Joint Test Action Group (ANSI/ICEEE Std. 1149.1-1990)         |  |

| kbps        | Kilobits per second                                           |  |

| LAN         | Local Area Network                                            |  |

| MB/s        | Megabytes per second                                          |  |

| Mbps        | Megabits per second                                           |  |

| MT/s        | Mega Transfers per second (throughput)                        |  |

| NVM         | Non Volatile Memory                                           |  |

| ОТР         | One Time Programmable                                         |  |

| PCM         | Pulse-coded Modulation                                        |  |

| PEG         | PCI Express Graphics                                          |  |

| Rx          | Receive                                                       |  |

| SCH         | System Controller Hub                                         |  |

| SDRAM       | Synchronous dynamic random access memory                      |  |

| SoC         | System-on-Chip                                                |  |

| SPI         | Serial peripheral interface                                   |  |

| Tx          | Transmit                                                      |  |

| UART        | Universal asynchronous receiver transmitter                   |  |

| USB         | Universal serial bus                                          |  |

| USB-OTG     | Universal serial bus on-the-go                                |  |

| USIM        | UMTS subscriber interface module                              |  |

| VCTCXO      | Voltage-controlled temperature-compensated crystal oscillator |  |

| WLAN        | Wireless Local Area Network                                   |  |

| XO          | Crystal oscillator                                            |  |

## 2 System Overview

#### 2.1 Highlights

Fit-PC3 and fit-PC3i are fully functional miniature computers based on AMD Embedded G-Series 64-bit dual core processor family.

Together with powerful AMD Radeon HD graphics engine, rich peripherals and connectivity options, completely fanless design delivers outstanding performance at lowest power consumption. The product offered in two processors SKUs, offering low-end and mid-end processing power. Fit-PC3 and fit-PC3i differs in a set of proposed connectivity and I/O options, as 2<sup>nd</sup> video output technology, number of LAN ports, Serial RS232 connectivity and readiness for cellular communication.

Performance Value ratio, low-power, rich I/O, miniature rugged design and cost competitiveness position fit-PC3 and fit-PC3i as an attractive solution for a wide range of applications – industrial control and automation, networking and communications infrastructures, media players and media centers, IPTV, infotainment system, digital signage and smart kiosks, gaming or small-footprint desktop replacement.

#### 2.2 Specifications

#### **Table 3 – Platform Specifications**

| Feature                                | Specifications                                             |  |

|----------------------------------------|------------------------------------------------------------|--|

| Processor                              | AMD Embedded G-Series (FT1): G-T56N/G-T40E                 |  |

|                                        | Dual core 64-bit                                           |  |

|                                        | Clock speed 1GHz – 1.65GHz (Note 1)                        |  |

|                                        | 18W TDP (Pro models)                                       |  |

|                                        | 6.4W TDP (LP models)                                       |  |

| Chipset                                | AMD Fusion Controller Hub (FCH) A55E                       |  |

| Memory                                 | Up to 16GB (2x 8GB) DDR3/DDR3L-1066/1333                   |  |

|                                        | 2x SO-DIMM 204-pin DDR3/DDR3L SDRAM memories               |  |

| Storage                                | 1x SATA up to 6 Gbps (SATA 3.0) for internal 2.5" HDD/SSD, |  |

|                                        | HDD to be used 5400rpm only                                |  |

|                                        | 1x mSATA slot up to 6 Gbps (SATA 3.0)                      |  |

|                                        | 2x eSATA ports up to 6 Gbps (SATA 3.0) (fit-PC3 only)      |  |

| Advanced AMD Virtualization Technology |                                                            |  |

| Technologies                           |                                                            |  |

| Operating Systems                      | Windows XP/7/8, 32-bit and 64-bit                          |  |

|                                        | Linux 32-bit and 64-bit                                    |  |

|                                        | Embedded OS                                                |  |

Table 4 – Display and Graphics Specifications

| Feature        | Specifications                              |                               |

|----------------|---------------------------------------------|-------------------------------|

|                | fit-PC3                                     | fit-PC3i                      |

| GPU            | AMD Radeon HD 6320/ HD 6250 (Pro/LP models) |                               |

|                | Dual display mode supported                 |                               |

| Video Output 1 | HDMI 1.4a up to 1920 x 1200 @               | HDMI 1.4a up to 1920 x 1200 @ |

|                | 60Hz                                        | 60Hz                          |

| Video Output 2 | DisplayPort 1.1a up to 2560 x               | HDMI 1.4a up to 1920 x 1200 @ |

|                | 1600 @ 60Hz                                 | 60Hz                          |

#### **Table 5 – Audio Specifications**

| Feature              | Specifications                       |  |

|----------------------|--------------------------------------|--|

| Codec                | Realtek ALC888-VC2 HD audio codec    |  |

| Audio Output         | Analog stereo output                 |  |

|                      | Digital 7.1+2 channels S/PDIF output |  |

|                      | 3.5mm jack                           |  |

| Audio Input          | Analog stereo Microphone input       |  |

| Digital S/PDIF input |                                      |  |

|                      | 3.5mm jack                           |  |

## **Table 6 – Networking Specifications**

| Feature  | ure Specifications                               |                                       |

|----------|--------------------------------------------------|---------------------------------------|

|          | fit-PC3                                          | fit-PC3i                              |

| LAN      | 1x GbE LAN ports (extendable up to 5)            | 2x GbE LAN ports (extendable up to 6) |

|          | LAN1: Realtek RTL8111F-CG GbE                    | LAN1: Realtek RTL8111F-CG GbE         |

|          | controller (RJ-45)                               | controller (RJ-45)                    |

|          | LAN2: N/A                                        | LAN2: Realtek RTL8111F-CG GbE         |

|          |                                                  | controller (RJ-45)                    |

|          | LAN3-6: Depends on FACE Module                   | LAN3-6: Depends on FACE Module        |

|          | (Note 2)                                         |                                       |

| Wireless | WLAN 802.11 b/g/n (2.4GHz Qcom Q802XRN5B module) |                                       |

|          | Bluetooth 3.0 + HS                               |                                       |

**Table 7 – Connectivity Specifications**

| Feature     | Specifications                      |                            |  |  |  |

|-------------|-------------------------------------|----------------------------|--|--|--|

|             | fit-PC3                             | fit-PC3i                   |  |  |  |

| USB         | 6x USB 2.0 (Note 3)                 | 8x USB 2.0 (Note 3)        |  |  |  |

|             | 2x USB 3.0                          |                            |  |  |  |

|             |                                     |                            |  |  |  |

| Serial      | 1x RS232 serial communication       | N/A                        |  |  |  |

|             | COM1: Serial port (u mini serial)   |                            |  |  |  |

| Special I/O | N/A                                 | 1x micro SIM slot (6 pins) |  |  |  |

|             |                                     |                            |  |  |  |

| Expansion   | Half-size mini-PCle socket          |                            |  |  |  |

|             | Full-size mini-PCle socket (Note 5) |                            |  |  |  |

Table 8 – Mechanical and Environmental Specifications

| Feature            | Specifications                           |

|--------------------|------------------------------------------|

| Input Voltage      | Unregulated 10 – 15VDC input (Note 6)    |

| Power Consumption  | 9W – 24W (Pro models)                    |

|                    | 7W – 15W (LP models)                     |

| Operating          | 1. Commercial                            |

| Temperatures       | HDD models: 0°C – 50°C                   |

|                    | SSD models: 0°C – 70°C                   |

|                    | 2. Extended (TE)                         |

|                    | SSD models only: -20°C – 70°C            |

|                    | 3. Industrial (TI)                       |

|                    | SSD models only: -40°C – 70°C            |

| Enclosure Material | Die Cast Aluminum                        |

| Cooling            | Passive Cooling Fanless Design           |

| Dimensions         | 19cm x 16cm x 4cm (Pro models)           |

|                    | 19cm x 16cm x 2.5cm (LP models)          |

| Weight             | 1100/1050gr (Pro/LP models respectively) |

#### Notes:

- 1. For full processors specifications based on fit-PC3/3i model, please refer to models and platform SKU *Table 9*.

- 2. Option for additional 4x GbE LAN ports. LAN3-6 based on FACE Module installed:

- a. FM-4USB: N/A

- b. FM-1LAN: LAN3 RTL8111F-CG GbE controller (RJ-45), LAN4-6: N/A

- c. FM-4LAN: Intel 82574 GbE Controller (RJ-45)

- d. FM-POE: Intel 82574 or I211AT GbE Controller (RJ-45)

- 3. Up to 4x additional USB2.0 on front panel based on FACE Module installed.

- 4. FACE Module HW specifications document Table 1.

- 5. Shared with mSATA. Refer to *Figure 17*.

- 6. Nominal input voltage: 12V

### 2.3 System Block Diagram

Fit-PC3 and fit-PC3i systems Top Level Block Diagrams are shown below. Later chapters in this document describe functions and entities shown in the below diagrams.

Figure 1 – fit-PC3 Top Level Block Diagram

Figure 2 – fit-PC3i Top Level Block Diagram

#### 2.4 Models and Platform SKUs

Table 9 - Models and Platform SKUs

| Model      | Pro                 | LP                  |

|------------|---------------------|---------------------|

| Processor  | AMD Embedded G-T56N | AMD Embedded G-T40E |

| Core Clock | 1.65GHz             | 1.0GHz              |

| Cores      | 64-bit dual core    | 64-bit dual core    |

| TDP        | 18W                 | 6.4W                |

| Chipset    | AMD FCH A55E        | AMD FCH A55E        |

| Graphics   | AMD Radeon HD 6320  | AMD Radeon HD 6250  |

Note: Table 9 refers to fit-PC3 and fit-PC3i system architectures.

### 3 Platform

#### 3.1 Processor

The AMD Embedded G-Series processor is the world's first integrated circuit to combine a low-power CPU and a discrete-level GPU into a single embedded Accelerated Processing Unit (APU). This unprecedented level of graphics integration builds a new foundation for high performance multi-media content delivery in a small form factor and power efficient platform for a broad range of embedded designs. Based on a power-optimized core, the AMD Embedded G-Series platform delivers levels of performance in a compact BGA package that is ideal for low power designs in embedded applications.

#### 3.1.1 Processor Features

This section lists the features and design capabilities of the AMD Embedded G-Series processor:

- Two high performance integrated x86 execution cores

- A 32-kB instruction and 32-KB data first-level cache (L1) for each core

- A 512-kB shared instruction / data second-level cache (L2) for each core

- Compatible with Existing 32-bit x86 and 64-bit AMD64 Code Base

- Support for SSE, SSE2, SSE3, SSE4A, SSSE3, MMX™, and legacy x86 instructions

- AMD 64-bit floating-point accelerator

- AMD Virtualization™ technology (AMD-V™)

- Integrated Memory Controller

- 64-bit DDR3 SDRAM controller operating at throughputs up to 1333 MT/s

- Theoretical max BW of 8.53 GB/s assuming DDR3 SDRAM 1066 MT/s

- Theoretical max BW of 10.65 GB/s assuming DDR3 SDRAM 1333 MT/s

- Integrated graphics processor

#### 3.2 Graphics Processor

This section lists the graphics features available for the AMD Embedded G-Series processor.

#### 3.2.1 Graphics Features

- AMD Radeon HD 6320 GPU Core architecture for Pro models

- AMD Radeon HD 6250 GPU Core architecture for LP models

- Dedicated graphics memory controller

- 2D Acceleration

- Highly-optimized 128-bit engine, capable of processing multiple pixels per clock

- 3D Acceleration

- DirectX® 11 compliant, including full speed 32-bit floating point per component operations

- Support for OpenCL™ 1.1

- Support for OpenGL 3.2 and 2.1

- Motion Video Acceleration Features

- Dedicated hardware (UVD 3) for H.264, MPEG4 Part 2, VC-1, and MPEG2 decode

- Microsoft DirectX video acceleration (DXVA) API (application programming interface) for Windows operating system

- Video scaling and YCrCb to RGB color space conversion for video playback and fully adjustable color controls

- Motion adaptive and vector based de-interlacing filter eliminates video artifacts caused by displaying interlaced video on non-interlaced displays, and by analyzing image and using optimal de-interlacing functions on a per-pixel basis

- HD HQV and SD HQV support: noise removal, detail enhancement, color enhancement, cadence detection, sharpness, and advanced de-interlacing

- Super up-conversion for SD to HD resolutions

#### 3.2.2 Display Interface

Display interface is fully integrated inside the Accelerated Processing Unit (APU). The APU houses memory interface, display planes, pipes, transcoders and display interface. The number of planes, pipes, and transcoders decide the number of simultaneous and concurrent display devices that can be driven on a platform. Fit-PC3/3i APU system architecture provides one Analog and two Digital Ports. Each Digital Port can transmit data according to one or more protocols. Fit-PC3 Digital Ports configured to drive natively HDMI/DVI and DisplayPort\*. Fit-PC3i Digital Ports configured to drive two HDMI/DVI displays. Each digital port has control signals that may be used to control, configure and/or determine the capabilities of an external device. Fit-PC3/3i design supports one, two or three simultaneous independent and concurrent display configurations, when two displays supported natively and for additional 3<sup>rd</sup> display provision is given.

For further display interface information refer to sections  $5.3\ and\ 5.4$  .

## 3.2.3 APU PCI Express\* Controller

The APU provides up to 4 PCI Express Root Ports, supporting the PCI Express Base Specification, Revision 2.0. Each Root Port x1 lane supports up to 5 Gbps bandwidth in each direction (10 Gbps concurrent). APU supports 4x1 or 1x4 PCI Express link. Supports L0s and L1 link power states for power saving.

#### 3.3 Chipset

The FCH provides extensive I/O support. Functions and capabilities include:

- Unified Media Interface (UMI)

- PCI Express\* Base Specification, Rev 2.0 support up to x4 ports with transfers up to 5 GT/s

- PCI Local Bus Specification, Revision 2.3 support for 33 MHz PCI operations

- 4 OHCl and 3 EHCl host controllers to support 14x USB2.0 ports and 2x USB1.1 ports

- Enhanced DMA controller, interrupt controller, and timer functions

- Integrated SATA host controllers within dependent DMA operation on six ports

- System Management Bus (SMBus) controller, with additional support for I2C devices

- Integrated Clock Controller

- Low Pin Count (LPC) interface

- High Definition Audio

#### 3.3.1 Unified Media Interface (UMI)

Unified Media Interface (UMI) is the chip-to-chip connection between the processor and FCH. This high-speed interface integrates advanced priority-based servicing allowing for concurrent traffic and true isochronous transfer capabilities. Base functionality is completely software-transparent, permitting current and legacy software to operate normally.

- 1-, 2-, or 4-lane Unified Media Interface connecting the FCH with the APU

- Automatic detection of lane configuration on boot-up

- Dynamic lane width up/down configuration on detecting bandwidth requirement

- Supports transfer rate of up to 5.0 GT/s per lane

- Clock speed can be locked at 2.5 GHz for power saving

#### 3.3.2 FCH PCI Express\* Controller

The FCH provides up to 4 PCI Express Root Ports, supporting the PCI Express Base Specification, Revision 2.0. Each Root Port x1 lane supports up to 5 Gbps bandwidth in each direction (10 Gbps concurrent). PCI Express Root Ports can independently be configured to support four x1s, two x2s, one x2 and two x1s, or one x4 port widths. Supports L0s and L1 link power states for power saving.

Refer to section 5.1 for detailed feature set.

#### 3.3.3 PCI Host Bus Controller

The PCI Bridge supports up to four PCI slots. The PCI Bridge runs at 33 MHz and can support CLKRUN# function with individual clock override (option for not stopping specific PCICLK). In addition, it has the capability to hide individual PCI devices. The FCH has a strapping option that allows loading of the boot codes from the PCI bus on the very first boot (first boot after RSMRST#). Subsequent boots will revert back to the ROM selection determined by the ROM straps or PMIO programming. This allows system manufacturers to populate the motherboard with a blank flash device (for BIOS) and use this option to program it. This is particularly useful for systems built without a socket for the BIOS ROM.

- Supports PCI bus at 33MHz

- Supports PCI Rev. 2.3 specification

- Supports up to 4 bus master devices

- Supports 40-bit addressing

- Interrupt steering supported for plug-n-play devices

- Supports concurrent PCI operations

- BIOS/hardware support to hide PCI device

- Supports spread spectrum

#### 3.3.4 Serial ATA (SATA) Controller

The integrated Serial ATA controller processes host commands and transfers data between the host and Serial ATA devices. It supports six independent Serial ATA channels. Each channel has its own Serial ATA bus and supports one Serial ATA device. With respect to the transfer rate, the integrated SATA controller supports First generation (1.5 Gbps), Second generation (3 Gbps), and Third generation (6 Gbps) SATA ports. Refer to *Figure 3* for FCH SATA block structure.

The SATA controller can operate in three modes:

- All six channels are configured as SATA AHCI mode.

- All six channels are configured as IDE mode. In this configuration, the SATA controller is configured into two IDE controllers, with the programming interface of channel 0 to 3 under the first IDE controller, and that of channel 4 and 5 under the second IDE controller.

- Four channels (channel 0 to 3) are configured as SATA AHCI and two channels (channel 4 and 5) are configured as IDE mode. In this configuration, the programming interface of channel 4 and 5 are under the IDE controller.

Figure 3 – Block Diagram for the SATA Module

#### 3.3.4.1 AHCI

The FCH provides hardware support for Advanced Host Controller Interface (AHCI), a standardized programming interface for SATA host controllers. Platforms supporting AHCI may take advantage of performance features such as no master/slave designation for SATA devices—each device is treated as a master—and hardware assisted native command queuing. AHCI also provides usability enhancements such as Hot-Plug. AHCI requires appropriate software support (such as, an AHCI driver) and for some features, hardware support in the SATA device or additional platform hardware.

#### 3.3.5 Low Pin Count (LPC) Bridge

The Low Pin Count (LPC) bus interface is a cost-efficient, low-speed interface designed to support low-speed legacy (ISA, X-bus) devices. The LPC interface essentially eliminates the need of ISA and X-bus in the system. A typical setup of the system with LPC interface is shown in *Figure 4*. Here the ISA bus is internal to FCH and is used for connecting to the legacy Direct Memory Access (DMA) logic. The LPC host controller is typically integrated into the FCH. It connects to the internal A-Link bus on one side and the LPC and Serial Peripheral Interface (SPI) buses on the other side.

The ISA interface is only used for legacy DMA operation.

Figure 4 - Typical LPC Bus System

Examples of LPC devices include Super I/O (disk controller, keyboard controller), BIOS RAM, audio, Trusted Platform Module (TPM), and system management controller. A BIOS ROM can also be populated on the SPI interface. The Hudson-E1 FCH can support an LPC or SPI type BIOS ROM.

LPC host controller has the A-Link bus on one side and the LPC bus on the other. The host controller supports memory and I/O read/write, DMA read/write, and bus master memory I/O read/write. It supports up to two bus masters and seven DMA channels.

Figure 5 – Block Diagram of LPC Module

#### 3.3.6 Universal Serial Bus (USB) Controllers

The FCH contains 4 OHCl and 3 EHCl host controllers to support 14 USB 2.0 ports that support USB high-speed signaling and 2 dedicated USB 1.1 ports. High-speed USB 2.0 allows data transfers up to 480 Mbps. Supports ACPI S1  $^{\sim}$  S4, USB keyboard/mouse functionality for legacy Operating Systems, USB debug port and individual port disable capability.

Figure 6 – USB Controllers Block Diagram

#### 3.3.7 RTC

The Real Time Clock (RTC) updates the computer's time and generates interrupts for periodic events and pre-set alarm. The RTC also makes hardware leap year corrections. The FCH's RTC includes a 256-byte CMOS RAM, which is used to store the configuration of a computer such as the number and type of disk drive, graphics adapter, base memory, checksum value, etc.

The internal RTC is made of two parts—one part is an analog circuit, powered by a battery VBAT, and the other is a digital circuit, powered by a main power VDD. Figure 7 shows the block diagram of the internal RTC. The FCH has added hardware-based daylight saving feature and makes adjustments (spring forward or fall back) at the designated dates/times. Both the date and hour for the daylight and standard time are fully programmable, allowing for different daylight saving dates and hours for different parts of the world.

Figure 7 - RTC Block Diagram

#### 3.3.8 GPIO

Various general purpose inputs and outputs are provided for custom system design. Refer to section 6.3.

#### 3.3.9 System Management Bus (SMBus)

The FCH contains SMBus Host interface that allows the processor to communicate with SMBus slaves. This interface is compatible with most I2C devices.

#### 3.3.10 High Definition Audio Controller

The High Definition (HD) Audio Controller communicates with the external HD Audio codec over the HD Audio Link. The FCH HD Audio Controller consists of four independent output DMA engines and four independent input DMA engines that are used to move data between system memory and the external codec. The controller can support up to four audio or modem codec in any combinations.

#### 3.3.11 Integrated Clock Controller

The FCH Hudson-E1 has an integrated system clock generator that can be used to generate the required system clocks, thus eliminating the need for an external clock generator. However, it does support a mode of operation that allows an external clock generator to be used in the system. The clock generator mode is selected by a power-on configuration strap. A simplified block diagram of the clock distribution for the integrated clock mode is shown in *Figure 8*.

Figure 8 - System Clock Generation

If FCH is in external clock mode, the clock sources it requires are a 25MHz crystal as internal PLL clock source, a 32-KHz crystal for the RTC, and a 100MHz differential clock pair for the PCIe reference clocks. In addition to the PCIe clocks, the chipset also uses the 100-MHz clock to generate various internal clocks. If Hudson-E1 is set to integrated clock mode, only a 25MHz crystal for master reference and a 32-KHz crystal for the RTC are required. Hudson-E1 will then generate all the system clocks needed, which include the APU reference clocks, the graphics clocks, the 25MHz clock for SATA, the 48MHz clocks for USB, and so on.

#### 3.4 System Memory

#### 3.4.1 Processor Integrated Memory Controller

Processor's Integrated Memory Controller (IMC) supports DDR3 and DDR3L protocols with single 64-bit wide channel, accessing one or two DIMMs. The IMC supports one or two, unbuffered non-ECC DDR3/DDR3L 204-pin SO-DIMMs.

G-T56N supports both DDR3/DDR3L-1066 and DDR3/DDR3L-1333 memories speeds.

G-T40E supports up to DDR3/DDR3L-1066 memories speeds.

Figure 9 - Memory Interface

Fit-PC3/3i system architecture provides support for 1.5V (DDR3) and 1.35V (DDR3L) power supplied SO-DIMMs. The adjustment of power rail for the memories and Memory Host Controller IOs is performed automatically without user or BIOS intervention. During boot SMBus Host Controller reads serial presence-detect (SPD) EEPROM on each SO-DIMM and adjust the voltage according to memory type. In case DDR3/DDR3L mixed memory modules are placed, the BUCK regulator will generate 1.5V output voltage, which may cause undesired behavior or permanent damage of the modules, unless DDR3L memory is tolerant to such voltages.

**Note**: It is important to keep both slots populated with the same memory technology.

#### 3.4.2 System Supported Memory

- DDR3 SDRAM memory with unbuffered SO-DIMM 204-pin modules

- Up to 16GB (2x 8GB) DDR3/DDR3L-1066/1333

- Supports up to two dual-rank SO-DIMMs

- Non-ECC, Unbuffered DDR3 SO-DIMMs only

- System Memory Interface I/O Voltage of 1.5V and 1.35V

- DDR3 SDRAM SO-DIMMs running at 1.5 V and 1.35V

- Single 64-bit wide channel

- Theoretical maximum memory bandwidth of:

- 8.53 GB/s assuming DDR3 SDRAM 1066 MT/s

- 10.65 GB/s assuming DDR3 SDRAM 1333 MT/s

- 1Gb, 2Gb, and 4Gb DDR3 SDRAM device technologies are supported

- Standard 1-Gb, 2-Gb, and 4-Gb technologies and addressing are supported for x16 and x8 devices. There is no support for memory modules with different technologies or capacities on opposite sides of the same memory module. If one side of a memory module is populated, the other side is either identical or empty.

- On-Die Termination (ODT)

**Table 10 – Supported Memory Technologies**

| Raw<br>Card<br>Version | DIMM<br>Capacity | DRAM<br>Device<br>Technology | DRAM<br>Organization | # of<br>DRAM<br>Devices | # of<br>Physical<br>Device<br>Ranks | # of<br>Row/Col<br>Address<br>Bits | # of<br>Banks<br>Inside<br>DRAM | Page<br>Size |

|------------------------|------------------|------------------------------|----------------------|-------------------------|-------------------------------------|------------------------------------|---------------------------------|--------------|

| Α                      | 2 GB             | 2 Gb                         | 128 M x 16           | 8                       | 2                                   | 14/10                              | 8                               | 8K           |

|                        | 4 GB             | 4 Gb                         | 256 M x 16           | 8                       | 2                                   | 15/10                              | 8                               | 8K           |

|                        | 1 GB             | 1 Gb                         | 128 M x 8            | 8                       | 1                                   | 14/10                              | 8                               | 8K           |

| В                      | 2 GB             | 2 Gb                         | 256 M x 8            | 8                       | 1                                   | 15/10                              | 8                               | 8K           |

|                        | 4 GB             | 4 Gb                         | 512 M x 8            | 8                       | 1                                   | 16/10                              | 8                               | 8K           |

| С                      | 1 GB             | 2 Gb                         | 128 M x 16           | 4                       | 1                                   | 14/10                              | 8                               | 8K           |

|                        | 2 GB             | 4 Gb                         | 256 M x 16           | 4                       | 1                                   | 15/10                              | 8                               | 8K           |

|                        | 2 GB             | 1 Gb                         | 128 M x 8            | 16                      | 2                                   | 14/10                              | 8                               | 8K           |

| F                      | 4 GB             | 2 Gb                         | 256 M x 8            | 16                      | 2                                   | 15/10                              | 8                               | 8K           |

|                        | 8 GB             | 4 Gb                         | 512 M x 8            | 16                      | 2                                   | 16/ 10                             | 8                               | 8K           |

Table 11 – Supported Max Memory Size per SO-DIMM

| Platform | Package | Memory      | Max Size<br>per DIMM<br>[GB] |

|----------|---------|-------------|------------------------------|

|          |         | SODIMM RC A | 4                            |

| Mobile   | rPGA    | SODIMM RC B | 4                            |

| Mobile   |         | SODIMM RC C | 2                            |

|          |         | SODIMM RC F | 8                            |

#### 3.4.3 System Memory Timing Support

The IMC supports the following Speed Bins, CAS Write Latency (CWL), and command signal mode timings on the main memory interface:

- tCL = CAS Latency

- tRCD = Activate Command to READ or WRITE Command delay

- tRP = PRECHARGE Command Period

- CWL = CAS Write Latency

- Command Signal modes = 1N indicates a new command may be issued every clock and 2N indicates a new command may be issued every 2 clocks. Command launch mode programming depends on the transfer rate and memory configuration.

Table 12 – DDR3 System Memory Timing Support

| Segment                  | Transfer<br>Rate<br>(MT/s) | tCL<br>(tCK) | tRCD<br>(tCK) | tRP<br>(tCK) | CWL<br>(tCK) | DPC | CMD<br>Mode |

|--------------------------|----------------------------|--------------|---------------|--------------|--------------|-----|-------------|

| Dual Core                | 1066                       | 7            | 7             | 7            | 6            | 1   | 1N/2N       |

| Standard<br>Voltage (SV) | 1000                       | 8            | 8             | 8            | 6            | 1   | 1N/2N       |

|                          | 1333                       | 9            | 9             | 9            | 7            | 1   | 1N/2N       |

#### 3.4.4 System Memory Organization Modes

The IMC supports single-channel organization mode only.

#### 3.4.5 Rules for Populating Memory Slots

The frequency and latency timings of the system memory is the lowest supported frequency and slowest supported latency timings of all memory SO-DIMM modules placed in the system.

### 3.5 Storage

Fit-PC3 and fit-PC3i supports various types of storage devices due to advanced FCH SATA Host Controller capabilities and I/O availability, described in section 3.3.4. Supported devices include HDD and SSD storage devices in 2.5" form factor. HDD limited to 5400rpm only due to power dissipation reasons. mSATA NAND Flash solid state drive modules supported as well and share mini PCIe full size slot. For detailed system architecture refer to section 6.1.

In addition, fit-PC3 offers two eSATA connectors, available on the back panel which allow connection of external storage drives. eSATA connectivity provide signaling only, when power to the external drives must be supplied externally.

Fit-PC3 and fit-PC3i, SATA system diagram is show in *Figure 10 – SATA Interface*.

Figure 10 - SATA Interface

## 3.5.1 Certified storage devices

## 3.5.1.1 HDD examples

## Table 13 – WD Scorpio Blue HDD series

| Specifications                                               | 1 TB                   | 1 TB                                     | 750 GB               | 750 GB                                   | 500 GB                                   |

|--------------------------------------------------------------|------------------------|------------------------------------------|----------------------|------------------------------------------|------------------------------------------|

| Model number                                                 | WD10SPCX               | WD10JPVX<br>WD10JPVT                     | WD7500LPCX           | WD7500BPVX<br>WD7500BPVT                 | WD5000LPVX<br>WD5000LPVT                 |

| Interface                                                    | SATA 6 Gb/s            | SATA 6 Gb/s (JPVX)<br>SATA 3 Gb/s (JPVT) | SATA 6 Gb/s          | SATA 6 Gb/s (BPVX)<br>SATA 3 Gb/s (BPVT) | SATA 6 Gb/s (LPVX)<br>SATA 3 Gb/s (LPVT) |

| Formatted capacity <sup>1</sup>                              | 1,000,204 MB           | 1,000,204 MB                             | 750,156 MB           | 750,156 MB                               | 500,107 MB                               |

| User sectors per drive                                       | 1,953,525,168          | 1,953,525,168                            | 1,465,149,168        | 1,465,149,168                            | 976,773,168                              |

| Advanced Format (AF)                                         | Yes                    | Yes                                      | Yes                  | Yes                                      | Yes                                      |

| Form factor                                                  | 2.5-inch               | 2.5-inch                                 | 2.5-inch             | 2.5-inch                                 | 2.5-inch                                 |

| RoHS compliant <sup>2</sup>                                  | Yes                    | Yes                                      | Yes                  | Yes                                      | Yes                                      |

| Performance                                                  |                        |                                          |                      |                                          |                                          |

| Data transfer rates                                          |                        |                                          |                      |                                          |                                          |

| Interface speed                                              | 6 Gb/s                 | 6 Gb/s (JPVX)<br>3 Gb/s (JPVT)           | 6 Gb/s               | 6 Gb/s (BPVX)<br>3 Gb/s (BPVT)           | 6 Gb/s (LPVX)<br>3 Gb/s (LPVT)           |

| Internal transfer rate (max)                                 | 140 MB/s               | 144 MB/s                                 | 140 MB/s             | 138 MB/s                                 | 147 MB/s                                 |

| Cache (MB)                                                   | 16                     | 8                                        | 16                   | 8                                        | 8                                        |

| Average latency (ms)                                         | 5.5                    | 5.5                                      | 5.5                  | 5.5                                      | 5.5                                      |

| Rotational speed (RPM)                                       | 5400                   | 5400                                     | 5400                 | 5400                                     | 5400                                     |

| Average drive ready time (sec)                               | 2.8                    | 3.0 (JPVX) / <3.5 (JPVT)                 | 2.8                  | 3.0 (BPVX) / 4.0 (BPVT)                  | 2.8 (LPVX) / <3.5 (LPVT)                 |

| Reliability/Data Integrity                                   |                        |                                          |                      |                                          |                                          |

| Load/unload cycles <sup>3</sup>                              | 600,000                | 600,000                                  | 600,000              | 600,000                                  | 600,000                                  |

| Non-recoverable read errors per bits read                    | <1 in 10 <sup>14</sup> | <1 in 1014                               | <1 in 1014           | <1 in 1014                               | <1 in 1014                               |

| Limited warranty (years)4                                    | 2                      | 2                                        | 2                    | 2                                        | 2                                        |

| Power Management                                             |                        |                                          |                      |                                          |                                          |

| 5VDC ±10% (A, peak)                                          | 1.00                   | 1.00 (JPVX) / 0.900 (JPVT)               | 1.00                 | 1.00 (BPVX) / 0.975 (BPVT)               | 1.00 (LPVX) / 0.900 (LPVT)               |

| Average power requirements (W) Read/Write Idle Standby/Sleep | 1.7<br>0.57<br>0.18    | 1.4<br>0.59<br>0.18                      | 1.7<br>0.57<br>0.18  | 1.6<br>0.65<br>0.20                      | 1.4<br>0.55<br>0.13                      |

| Environmental Specifications <sup>5</sup>                    |                        |                                          |                      |                                          |                                          |

| Temperature (°C) Operating Non-operating                     | 0 to 60<br>-40 to 65   | 0 to 60<br>-40 to 65                     | 0 to 60<br>-40 to 65 | 0 to 60<br>-40 to 65                     | 0 to 60<br>-40 to 65                     |

| Shock (Gs) Operating (2 ms, read) Non-operating              | 350<br>1000 (2 ms)     | 400<br>1000 (2 ms)                       | 350<br>1000 (2 ms)   | 350<br>1000 (2 ms)                       | 400<br>1000 (2 ms)                       |

| Acoustics (dBA) <sup>6</sup><br>Idle<br>Seek (average)       | 20<br>21               | 24<br>25                                 | 20<br>21             | 24<br>25                                 | 17<br>22                                 |

| Physical Dimensions                                          |                        |                                          |                      |                                          |                                          |

| Height (in./mm, max)                                         | 0.28/7.0               | 0.374/9.50                               | 0.28/7.0             | 0.374/9.50                               | 0.28/7.0                                 |

| Length (in./mm, max)                                         | 3.94/100.20            | 3.94/100.20                              | 3.94/100.20          | 3.94/100.20                              | 3.94/100.20                              |

| Width (in./mm, ± .01 in.)                                    | 2.75/69.85             | 2.75/69.85                               | 2.75/69.85           | 2.75/69.85 2.75/69.85                    |                                          |

| Weight (lb./kg, ± 10%)                                       | 0.21/0.09              | 0.27/0.12                                | 0.21/0.09            | 0.34/0.15                                | 0.20/0.09                                |

Table 14 – WD Scorpio Blue HDD series (cont.)

| Specifications                                               | 500 GB               | 500 GB               | 320 GB                                   | 320 GB               | 250 GB                                   | 250 GB               |

|--------------------------------------------------------------|----------------------|----------------------|------------------------------------------|----------------------|------------------------------------------|----------------------|

| Model number                                                 | WD5000MPCK           | WD5000BPVT           | WD3200LPVX<br>WD3200LPVT                 | WD3200BPVT           | WD2500LPVX<br>WD2500LPVT                 | WD2500BPVT           |

| Interface                                                    | SATA 6 Gb/s          | SATA 3 Gb/s          | SATA 6 Gb/s (LPVX)<br>SATA 3 Gb/s (LPVT) | SATA 3 Gb/s          | SATA 6 Gb/s (LPVX)<br>SATA 3 Gb/s (LPVT) | SATA 3 Gb/s          |

| Formatted capacity <sup>1</sup>                              | 500,107 MB           | 500,107 MB           | 320,072 MB                               | 320,072 MB           | 250,059 MB                               | 250,059 MB           |

| User sectors per drive                                       | 976,773,168          | 976,773,168          | 625,142,448                              | 625,142,448          | 488,397,168                              | 488,397,168          |

| Advanced Format (AF)                                         | Yes                  | Yes                  | Yes                                      | Yes                  | Yes                                      | Yes                  |

| Form factor                                                  | 2.5-inch             | 2.5-inch             | 2.5-inch                                 | 2.5-inch             | 2.5-inch                                 | 2.5-inch             |

| RoHS compliant <sup>2</sup>                                  | Yes                  | Yes                  | Yes                                      | Yes                  | Yes                                      | Yes                  |

| Performance                                                  |                      |                      |                                          |                      |                                          |                      |

| Data transfer rates                                          |                      |                      |                                          |                      |                                          |                      |

| Interface speed                                              | 6 Gb/s               | 3 Gb/s               | 6 Gb/s (LPVX)<br>3 Gb/s (LPVT)           | 3 Gb/s               | 6 Gb/s (LPVX)<br>3 Gb/s (LPVT)           | 3 Gb/s               |

| Internal transfer rate (max)                                 | 145 MB/s             | 136 MB/s             | 147 MB/s (LPVX)<br>109 MB/s (LPVT)       | 116 MB/s             | 147 MB/s (LPVX)<br>109 MB/s (LPVT)       | 116 MB/s             |

| Cache (MB)                                                   | 16                   | 8                    | 8                                        | 8                    | 8                                        | 8                    |

| Average latency (ms)                                         | 5.5                  | 5.5                  | 5.5                                      | 5.5                  | 5.5                                      | 5.5                  |

| Rotational speed (RPM)                                       | 5400                 | 5400                 | 5400                                     | 5400                 | 5400                                     | 5400                 |

| Average drive ready time (sec)                               | 2.8                  | 4.0                  | 2.8 (LPVX) / <3.5 (LPVT)                 | 4.0                  | 2.8 (LPVX) / <3.5 (LPVT)                 | 4.0                  |

| Reliability/Data Integrity                                   |                      |                      |                                          |                      |                                          |                      |

| Load/unload cycles <sup>3</sup>                              | 600,000              | 600,000              | 600,000                                  | 600,000              | 600,000                                  | 600,000              |

| Non-recoverable read errors per bits read                    | <1 in 1014           | <1 in 1014           | <1 in 1014                               | <1 in 1014           | <1 in 1014                               | <1 in 1014           |

| Limited warranty (years) <sup>4</sup>                        | 2                    | 2                    | 2                                        | 2                    | 2                                        | 2                    |

| Power Management                                             |                      |                      |                                          |                      |                                          |                      |

| 5VDC ±10% (A, peak)                                          | 0.900                | 0.950                | 1.00 (LPVX) / 0.900 (LPVT)               | 1.00                 | 1.00 (LPVX) / 0.900 (LPVT)               | 1.00                 |

| Average power requirements (W) Read/Write Idle Standby/Sleep | 1.5<br>0.55<br>0.15  | 1.6<br>0.65<br>0.20  | 1.4<br>0.55<br>0.13                      | 2.5<br>0.85<br>0.20  | 1.4<br>0.55<br>0.13                      | 2.5<br>0.85<br>0.20  |

| Environmental Specifications <sup>5</sup>                    |                      |                      |                                          |                      |                                          |                      |

| Temperature (°C)<br>Operating<br>Non-operating               | 0 to 60<br>-40 to 65 | 0 to 60<br>-40 to 65 | 0 to 60<br>-40 to 65                     | 0 to 60<br>-40 to 65 | 0 to 60<br>-40 to 65                     | 0 to 60<br>-40 to 65 |

| Shock (Gs) Operating (2 ms, read) Non-operating              | 400<br>1000 (2 ms)   | 350<br>1000 (2 ms)   | 400<br>1000 (2 ms)                       | 350<br>1000 (2 ms)   | 400<br>1000 (2 ms)                       | 350<br>1000 (2 ms)   |

| Acoustics (dBA) <sup>ii</sup><br>Idle<br>Seek (average)      | 15<br>17             | 22<br>25             | 17<br>22                                 | 22<br>25             | 17<br>22                                 | 22<br>25             |

| Physical Dimensions                                          |                      |                      |                                          |                      |                                          |                      |

| Height (in./mm, max)                                         | 0.20/5.0             | 0.374/9.50           | 0.28/7.0                                 | 0.374/9.50           | 0.28/7.0                                 | 0.374/9.50           |

| Length (in./mm, max)                                         | 3.95/100.30          | 3.94/100.20          | 3.94/100.20                              | 3.94/100.20          | 3.94/100.20                              | 3.94/100.20          |

| Width (in./mm, ± .01 in.)                                    | 2.75/69.85           | 2.75/69.85           | 2.75/69.85                               | 2.75/69.85           | 2.75/69.85                               | 2.75/69.85           |

| Weight (lb./kg, ± 10%)                                       | 0.16/0.07            | 0.22/0.10            | 0.20/0.09                                | 0.22/0.10            | 0.20/0.09                                | 0.22/0.10            |

Table 15 – Hitachi CinemaStar C5K750 HDD models

| Model(s)                                      | HCC547575A9E380        |  |  |

|-----------------------------------------------|------------------------|--|--|

|                                               | HCC547564A9E380        |  |  |

|                                               | HCC547550A9E380        |  |  |

| Configuration                                 |                        |  |  |

| Interface                                     | SATA 3Gb/s             |  |  |

| Capacity (GB) <sup>1</sup>                    | 750 / 640 / 500        |  |  |

| Sector size (bytes) <sup>2</sup>              | 512e                   |  |  |

| Recording zones                               | 24                     |  |  |

| Max. areal density (Gbits/sq. in.)            | 492                    |  |  |

| Performance                                   |                        |  |  |

| Data buffer (MB) <sup>3</sup>                 | 8                      |  |  |

| Rotational speed (RPM)                        | 5400                   |  |  |

| Latency average (ms)                          | 5.5                    |  |  |

| Media transfer rate (Mbits/sec, max.)         | 996                    |  |  |

| Interface transfer rate (MB/sec, max.)        | 300                    |  |  |

| Seek time, read (ms, typical) <sup>4</sup>    | 15                     |  |  |

| Reliability                                   |                        |  |  |

| Load/unload cycles                            | 600,000                |  |  |

| Power on Hours (POH) per month                | 730                    |  |  |

| Availability <sup>5</sup> (hrs/day x days/wk) | 24x7                   |  |  |

| Power                                         |                        |  |  |

| Requirement                                   | +5 VDC (+/-5%)         |  |  |

| Startup (W, peak, max.)                       | 3.5                    |  |  |

| Operating <sup>6</sup> (W, avg.)              | 1.5                    |  |  |

| Low power idle (W, avg.)                      | 0.5                    |  |  |

| Physical size                                 |                        |  |  |

| z-height (mm)                                 | 9.5                    |  |  |

| Dimensions (width x depth, mm)                | 70 x 100               |  |  |

| Weight (g, typical)                           | 102                    |  |  |

| Environmental (operating)                     |                        |  |  |

| Shock (half-sine wave)                        | 400G (2ms), 225G (1ms) |  |  |

| Operating temperature <sup>7</sup>            | 0° to 70° C            |  |  |

| Environmental (non-operating)                 |                        |  |  |

| Shock (half-sine wave)                        | 1000G (1ms)            |  |  |

| Ambient temperature                           | -40° to 65° C          |  |  |

| Acoustics (A-weighted sound power)            |                        |  |  |

| Idle (Bels, typical)                          | 2.4                    |  |  |

| Seek (Bels, typical)                          | 2.5                    |  |  |

#### **Table 16 – Seagate Momentus HDD series**

## Seagate® Momentus® 2.5" Internal Drive

Instant Add-on Storage

Interface SATA

Capacities 250GB, 320GB, 500GB, 640GB, 750GB

#### Momentus LP Drive - Energy Efficient, High Capacity Storage

Engineered specifically for low-power applications, the Momentus LP internal drive has a 5400RPM spindle speed and a 8MB cache to provide energy-efficient performance at whisper-quiet acoustic levels. With reduced power consumption and heat generation, this drive will reduce power costs up to 50% over the life of the system compared to standard drives. It is optimized for standard laptops and small form factor PCs.

- 5400RPM

- 8MB cache

- SATA 3Gb/s interface with Native Command Queueing

- QuietStep™ technology enables ultra-quiet load/unload acoustics

- Perpendicular recording technology increases performance and reliability

#### 3.5.1.2 mSATA SSD examples

Table 17 - Micron mSATA NAND Flash SSD

M500 mSATA NAND Flash SSD Features

## M500 mSATA NAND Flash SSD

## MTFDDAT120MAV, MTFDDAT240MAV, MTFDDAT480MAV

#### **Features**

- Micron® 20nm MLC NAND Flash

- · RoHS-compliant package

- · SATA 6 Gb/s interface

- · TCG/Opal 2.0-compliant self-encrypting drive

- · Hardware-based AES-256 encryption engine

- · ATA modes supported

- PIO mode 3, 4

- Multiword DMA mode 0, 1, 2

- Ultra DMA mode 0, 1, 2, 3, 4, 5

- · Industry-standard, 512-byte sector size support

- · Device Sleep (DEVSLP), extreme low power mode

- · Native command queuing support with 32-command slot support

- · ATA-8 ACS2 command set compliant

- · ATA security feature command set and password login support

- · Secure erase (data page) command set: fast and secure erase

- · Sanitize device feature set support

- Self-monitoring, analysis, and reporting technology (SMART) command set

- · Windows 8 drive telemetry

- · Adaptive thermal monitoring

- Performance<sup>1, 2</sup>

- PCMark® Vantage (HDD test suite score): up to 80,000

- Sequential 128KB READ: up to 500 MB/s

- Sequential 128KB WRITE: up to 400 MB/s

- Random 4KB READ: up to 80,000 IOPS

- Random 4KB WRITE: up to 80,000 IOPS

- READ/WRITE latency: 5ms/25ms (MAX)

- Reliability

- MTTF: 1.2 million device hours<sup>3</sup>

- Static and dynamic wear leveling

- Uncorrectable bit error rate (UBER): <1 sector per 1015 bits read

- · Low power consumption

- 150mW TYP<sup>4</sup>

- Endurance: Total bytes written (TBW) 72TB

- Capacity<sup>5</sup> (unformatted): 120GB, 240GB, 480GB

- Mechanical

- mSATA connector: 3.3V ±5%

- Caseless design: 50.80mm x 29.85mm x 3.75mm

- Weight: 10g (MAX)

- · Secure firmware update with digitally signed firmware image

- Operating temperature

- Commercial (0°C to +70°C)<sup>6</sup>

- Notes: 1. Typical I/O performance numbers as measured fresh-out-of-box (FOB) using lometer with a queue depth of 32 and write cache enabled

- 2. 4KB transfers used for READ/WRITE latency values.

- 3. The product achieves a mean time to failure (MTTF) based on population statistics not relevant to individual units.

- 4. Active average power measured during execution of MobileMark® with DIPM (deviceinitiated power management) enabled.

- 5. 1GB = 1 billion bytes; formatted capacity is

- 6. Drive on-board sensor temperature.

Warranty: Contact your Micron sales representative for further information regarding the product, including product warranties.

#### Table 18 – ACPI CMS2G-M SSD

| Specification                |                            |

|------------------------------|----------------------------|

| Model Name                   | CMS2G-M                    |

| Interface                    | SATA III 6Gb/s compatible  |

| NAND Flash Type              | MLC                        |

| Connector Type               | miniPCle mSATA             |

| External DRAM Buffer         | Yes                        |

| Capacity                     | 32GB~256GB                 |

| Sequential R/W (128KB, Typ.) | Max 530/330 MB/s           |

| Random R/W (4KB, Typ.)       | Max 94K/75K IOPS           |

| _ ,                          | Operating Temp.:0°C~+70°C  |

| Temperature                  | Storage Temp.: -40°C~+90°C |

| TRIM                         | Support                    |

| S.M.A.R.T. (Health Monitor)  | Support                    |

| Security Tool                | •                          |

| MTBF                         | > 1.2 million hours        |

| Vibration (Operating)        | 20G Peak, 7~2000Hz         |

| Shock                        | 1500G, 0.5ms               |

| Dimension (LxWxH)            | 50.8*29.85*3.7mm           |

| Weight                       | 8 gram                     |

| Warranty                     | 3 Year                     |

# 4 Peripherals

### 4.1 USB3.0 Host Controller

Fit-PC3/3i system architecture features USB3.0 connectivity via dedicated Host Controller from Texas Instruments. TUSB7320 is a USB 3.0 xHCl compliant host controller that supports up to four downstream ports. The TUSB7320 interfaces to the host system via a PCle x1 Gen 2 interface and provides Super Speed, high-speed, full-speed, or low-speed connections on the downstream USB ports.

The TUSB7320 target applications such as desktop and mobile computers, workstations, servers, Add-In Cards and Express Cards implementations and PCI Express based embedded applications.

#### Main Features

- USB 3.0 Compliant xHCl Host Controller

- PCIe x1 Gen2 interface

- Two downstream ports (USB3.0 and USB2.0 combined)

- Requires no external flash for default configuration

- Optional serial EEPROM for custom configuration

- Internal Spread Spectrum generation

- Adaptive receiver equalizer

#### Each Downstream Port

- May be independently enabled or disabled

- Has adjustments for transmit swing, De-Emphasis, and Equalization settings